工程配置

工程创建

新建文件夹

设置芯片信号

新建RTL工程

文件添加

添加Designed文件

暂时不做管脚分配

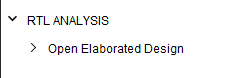

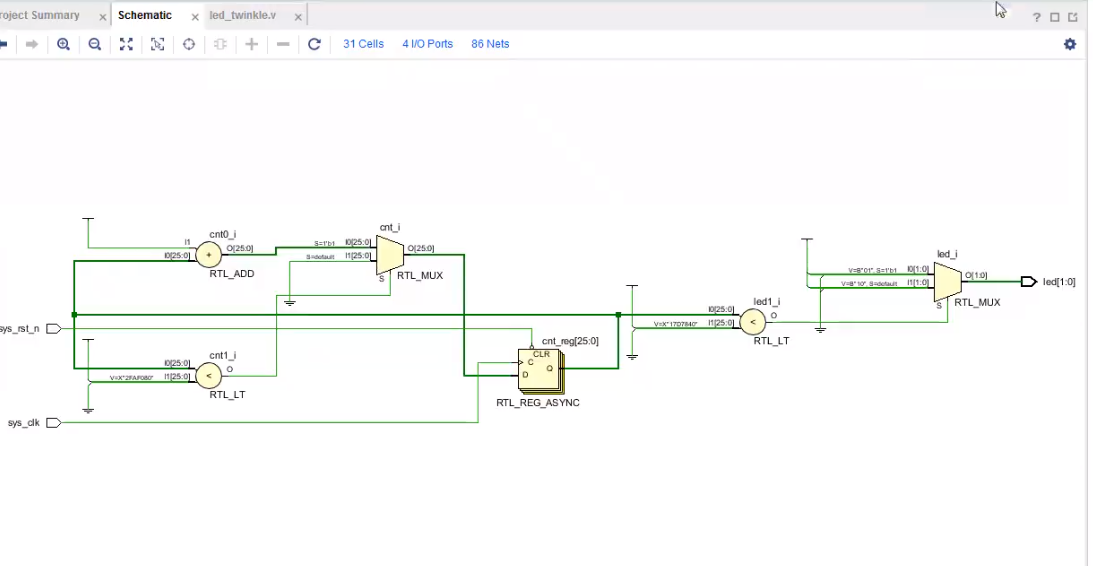

RTL Analysis

右上角切换 IO Planing视图

IO约束: 分配管脚 分配电平

保存管脚分配图(Constraint.xdc文件)

关闭RTL Analysis

设计实现

Synthesis(综合): 分配编译核心数目

生成比特流: 可在右上角或Project Manger查看进度

Open Hardware Mangerment

连接下载器 开发板 电脑

Program Device对FPGA编程

Vivado硬件调试

硬件调试简介

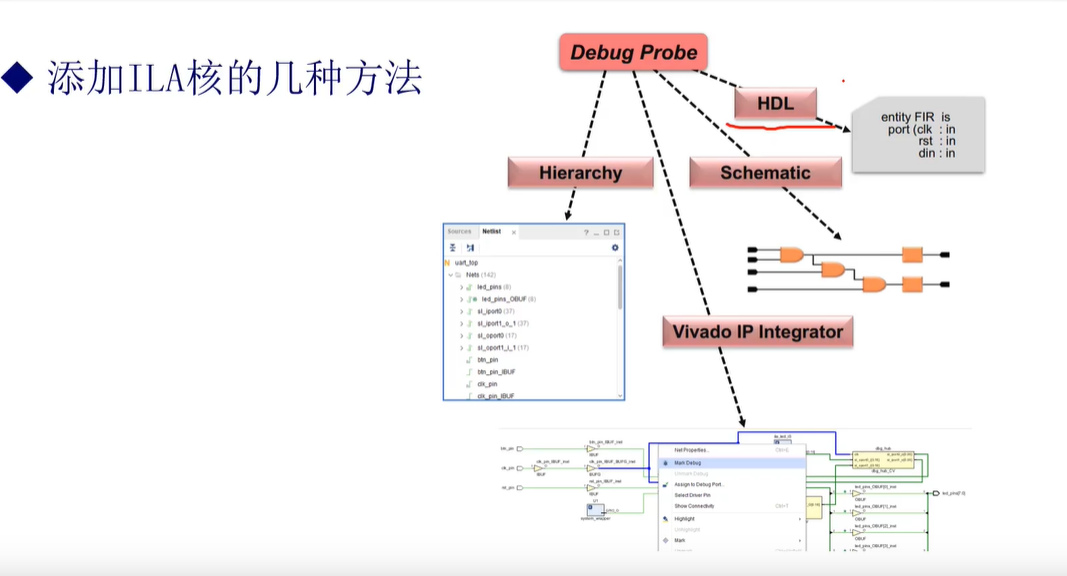

通过向FPGA中添加ILA VIO核实现硬件调试,并通过Jtag连接到PC

Integrate Logic Analyzer(ILA): 监控内部信号和端口信号

Virtual Input/Output(VIO): 实时监控驱动内部信号和端口信号

ILA 内部逻辑分析器

添加方法

HDL方法

综合之后,在网表(Netlist)中添加

HDL方法

IP Integrated

搜索ILA: System ILA不使用,用于IP"集成器"中,我们使用的的是IP的"调试设计"

选择模式: AXI Native(default)

选择probe数目和存储深度

配置Probe_Port位宽

选择OK

后配置Synthesis综合选项: Global和Out of context per IP(OOC模式)

选择OOC 时候,创建时候会被综合一次,综合整个工程时候不会被综合,Global模式每次都会被综合

例化

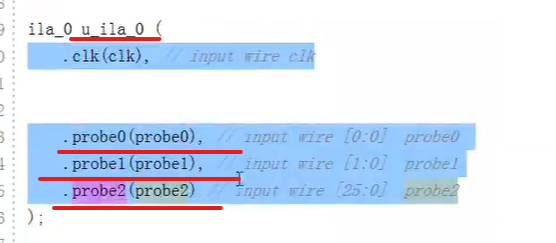

代码中"例化"将代码中端口同IP核中端口想连接

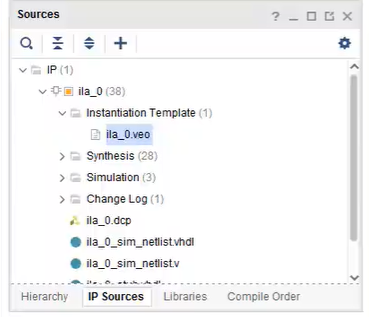

Source中选择IP Source

选择instantiation Template中veo文件

将例化模板拷贝到Designed文件

修改模板中的例化名 一般u_模块名

修改probe0 probe1 probe2 clk

综合方法

Synthesis之后,在网表里对应信号右键添加Mark Debug

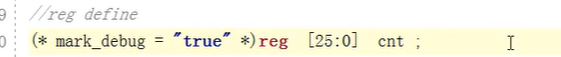

在Designed源文件中,添加属性,防止软件优化部分信号,并且自动将信号设为Debug

综合之后,相当于还是在网表文件中做修改(.xdc)

Setup Debug 选择观察的信号,并右键分配时钟(类似ILA设置)

设置采样设置等等

Vivado Simulator使用

仿真概述

硬件调试: 需要消耗FPGA资源

软件仿真: 一般不需要,且仿真需要提供Test Bench(tb)激励文件

参考文件: Vivado设计套件使用指南-仿真篇(UG900)

仿真分类: RTL仿真(仅针对代码功能,不考虑门延迟 线延迟) 时序仿真

常规只需要功能仿真

此处仿真使用(第一方Vivado Simulator)

创建TestBench激励文件

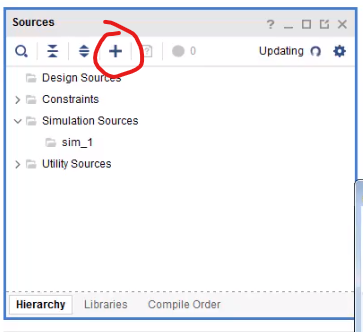

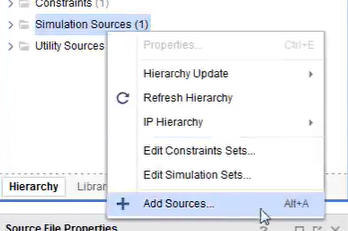

在Source-Simulator Source里右键Add Source

Create File: 一般文件命名tb_模块名.v

对于激励文件里自带的module,不需要输入输出端口

声明reg变量 wire变量

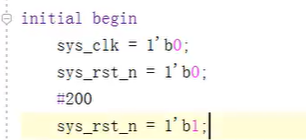

初始化initial begin...end

1'代表位宽 b代表进制

#200 指200ns由前面的timescale确定

timescale [单位]/[精度]

代码编写

always #10 sysclk=~sysclk

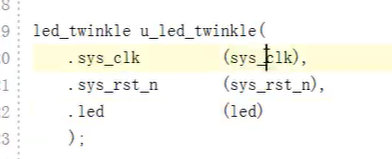

代码例化

相当于调用模块,并在对应接口处连线

开始仿真

仿真选项

行为仿真 综合功能仿真 综合时序 实现功能仿真 实现时序仿真

功能仿真实际上为一般指→行为方法

时序仿真实际上一般指→实现时序仿真

Setting中可修改默认的仿真时间

修改代码后(Designed)直接Relaunch Simulation即可

Scope:

tb模块(文件)

u例化模块: 此时以激励文件位主体,Designed文件是作为module被tb调用的

glbl 全局文件

Object: 默认只显示tb文件信号,需要u模块信号,需要在Scope中选中模块,并右键添加