时钟IP核MMCM(混合模式时钟管理) PLL(锁相环) 简介

参考文档: 7系列FPGA时钟资源(UG472)

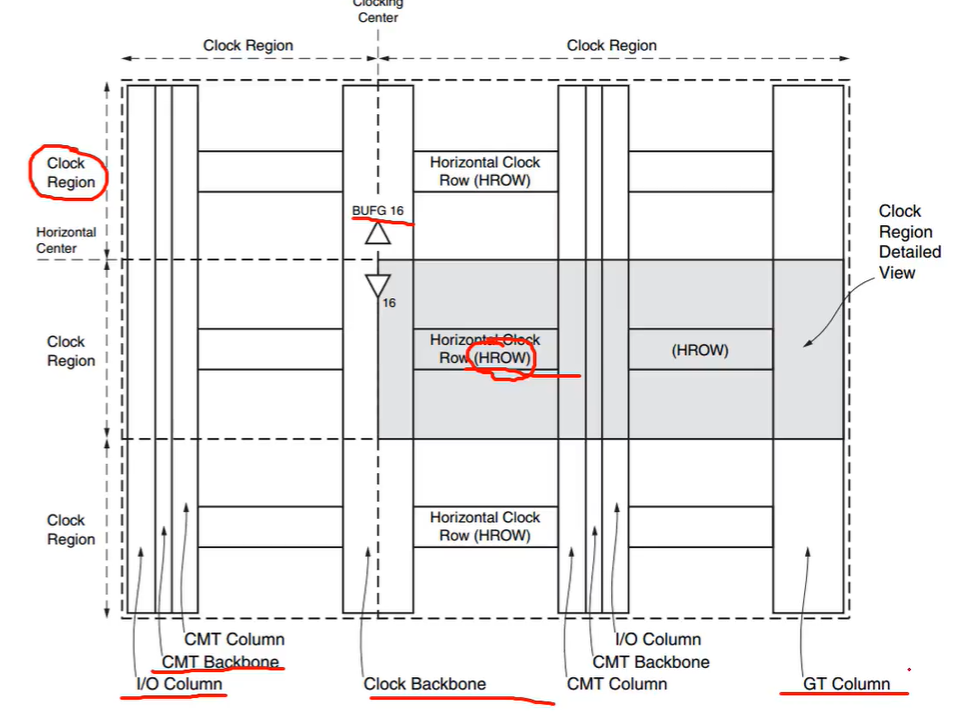

包括 全局时钟(Global) 区域时钟(Regional)

全局时钟: 专用全局网络 有专用时钟缓存和驱动结构→到其他逻辑资源(BRAM)延迟低

区域时钟: 只能驱动区域内部的时钟资源和IO口

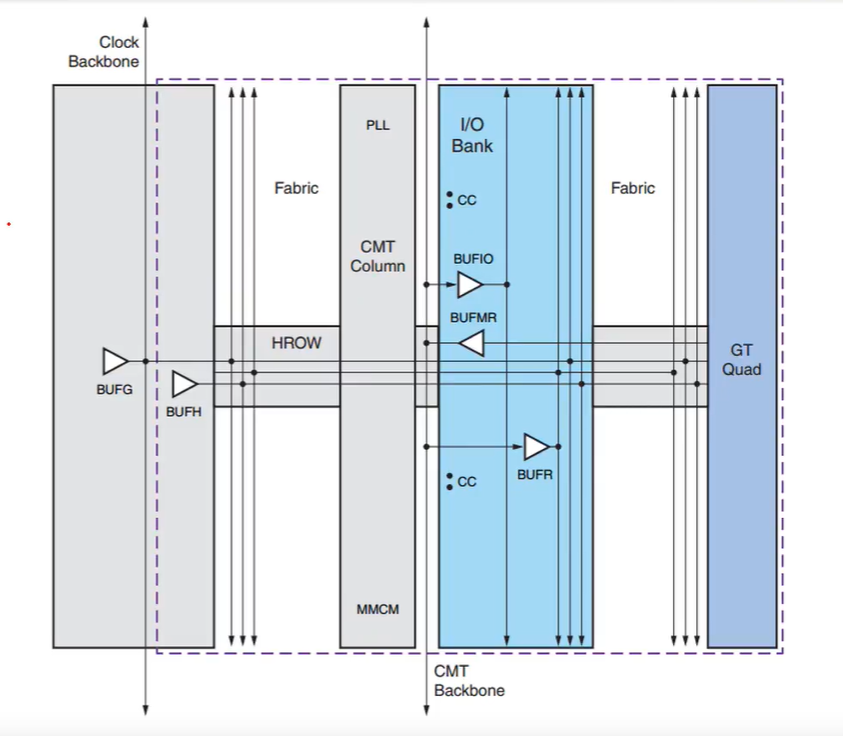

时钟结构图

BUFG: Buffer Global 全局时钟缓冲

BUFH: Buffer H(???) 水平时钟缓冲

BUFIO: Buffer IO IO时钟缓冲

BUFR: Buffer Region 区域时钟缓冲

BUFMR: Buffer Multi-Region多区域时钟缓冲

MMCM: Multi Mode Clock Controller 混合模式时钟管理器

PLL: 锁相环

CC: 时钟专用引脚(接外部输入)

SRCC仅本区域

MRCC相邻区域

P N区别: 可以接受差分信号,单端时钟仅能连到P端

BUF作用域

BUFG可以到达时钟域(Clock Region)任何角落,而BUFH只能到HROW左右相邻的时钟区域

BUFIO: 只能作用于IO区域,而不能在内部逻辑区域使用

BUFR: 只能作用于本区域,相当于BUFH阉割

BUFMR: 不仅可以作用于本区域,也可通过CMT Backbone作用相邻区域

CMT: MCMM PLL

Clock Management Tiles(CMT)

CMT简介

一个CMT 包括一个MMCM和一个PLL

7020 4个CMT \ 7010 2个CMT

Clock Frequency Synthesis时钟合成

Desked 倾斜校正

Jitter Filtering 过滤抖动

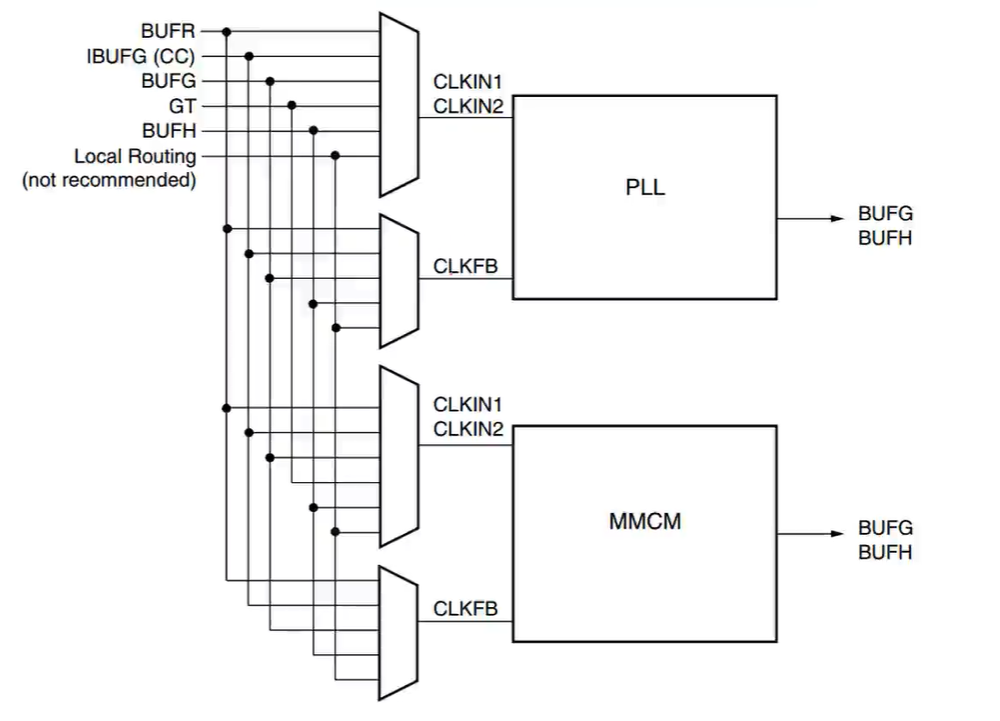

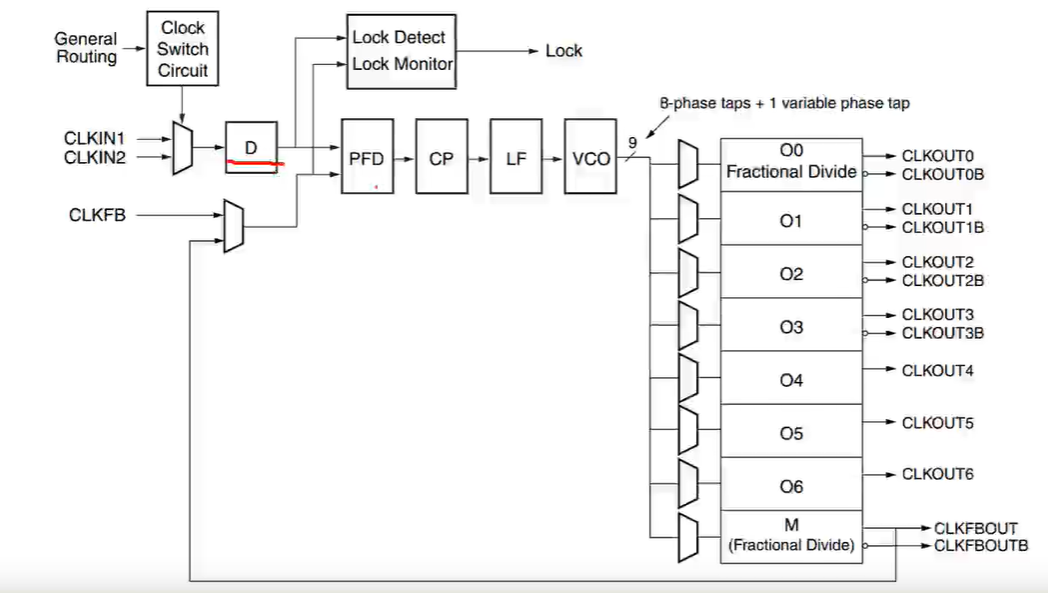

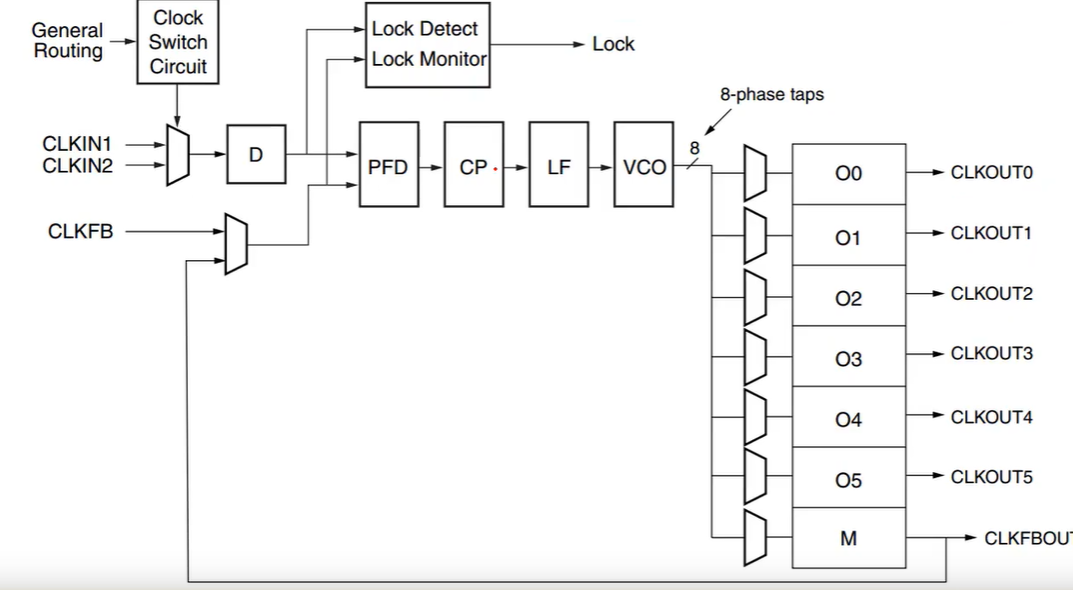

MCMM/PPLL内部结构

MCMM实际为PLL功能升级: 分数倍频率综合 反向时钟输出 动态时钟相位调整

D(可编程计数分频)→PFD(相位 频率检测器)→CP(电荷泵)→LF(环路滤波器)→VCO(压控振荡器)→Phase-Tab相位抽头

Lock信号: 锁相信号

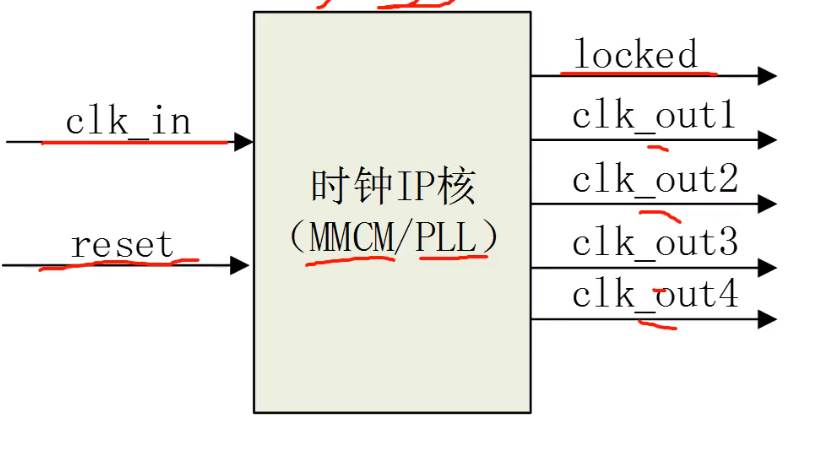

时钟IP核的使用

IP Category→Clock→Clock Wizard

Clock Wizard配置

Clock Option

Clock Monitor: 可以监控输入的时钟,一般不勾选

配置Feature 选择时钟源

Output Clocks

可能Request(理想要求)和Actual(实际上)不相同

可以修改Port Name

Driver修改,保持默认BUFG,时钟可以走全局网络

Reset,Lock信号配置,默认不变(注意Lock拉高后时钟才稳定)

MCMM配置

例化IP核