一.HDL简介

Hardware Description Language HDL 硬件描述语言

定义: 可以从不同层次描述数字电路结构和功能

不同层次: 指高层次(类C) 底层(类汇编)

和C异同

并行性: 各个模块同时开始工作,而C语言是串行

属于高级硬件描述,语法上类C

数字系统设计: 逻辑设计(前端)→电路实现(后端)→验证

前端: HDL编程,逻辑设计部分

后端: HDL→综合工具→门级别网表→和某种工艺的基本元件再对应→布局布线工具→电路结构

常见HDL

美中: Verilog HDL

欧洲: VHDL

FPGA设计也可采用原理图输入法

二.Verilog基础

逻辑值:

0: 表示GND

1: 表示VCC

X: 表示未知电平,但是1 或 0中一个

Z: 表示高阻态,外部无激励,属于悬空,不能判断1或0或其中任何中间

非1的其他值均为逻辑假

数字格式

[位宽] ' [d(dec)\b(binary)\h(16进制)\oOct)] 值

值中间可用下划线分割如

16'b1001_1010_1111_1001

如果没有指定 位宽和进制 默认为32'd

标识符

可用于定义 模块名 端口名 信号名(可理解为变量或常量)

可为 [a-z A-Z 0-9 $ _] 第一个字符为 字母或下划线

区分大小写:

代码规范

不建议大小写混合 内部信号全小写

下划线区分: 如cpu_addr

采用前缀或后缀: 如clk_50m clk_cpu

数据类型

类型简介

寄存器 线网 参数,其中寄存器 线网有实际的电路映射

寄存器

抽象数据存储单元,可以被幅值

初始值为 X(参见上面逻辑值)

赋值

只能被initial always赋值

always既可以组合逻辑也可时序逻辑

若语句为时序逻辑(即含有时钟信号),则实际上对应一个触发器

若仅为组合逻辑,对应实际连线

线网

表示结构实体(门)之间的物理连线

默认值为 Z

不指定数据类型默认为wire类型

不能存储值,值由驱动线网的器件决定

驱动线网的元器件

门

连续赋值语句

assign语句: 仅能描述组合逻辑

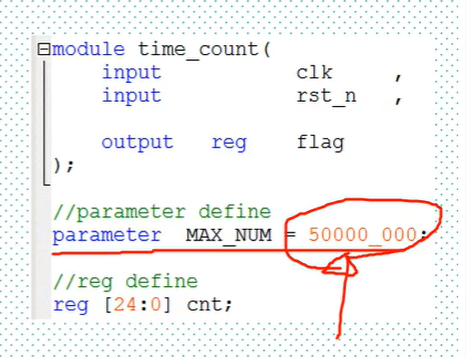

参数 parament

实际为常量

可用于表示状态机状态 数据位宽 延迟大小

模块调用时候可以传递参数

运算符

算数运算符: /小数部分省略

关系运算符:

位移运算符: 左右移动都是填0来补空缺

位拼接运算符: c = { a, b[3:0] }

三.Verilog语法

注释: 类C // 或 /*...*/

程序框架

基本设计单元为Block 模块:

一部分描述接口 一部分描述逻辑功能

程序包括: 端口定义 IO说明(可以和端口定义合并) 内部信号声明 功能定义

不可综合模块: 不对应实际的电路,例如仿真文件

接口描述

module block(a,b,c,d);

input a, b;

output c, d;

assign c = a | b ; /未指明类型默认为wire

assign d = a & b ;

endmodule

Copy

Verilog

功能定义

assign: 描述组合逻辑

always: 描述组合时序

实例化器件: 如 and #2 u1(q,a,b)

三种逻辑功能并行

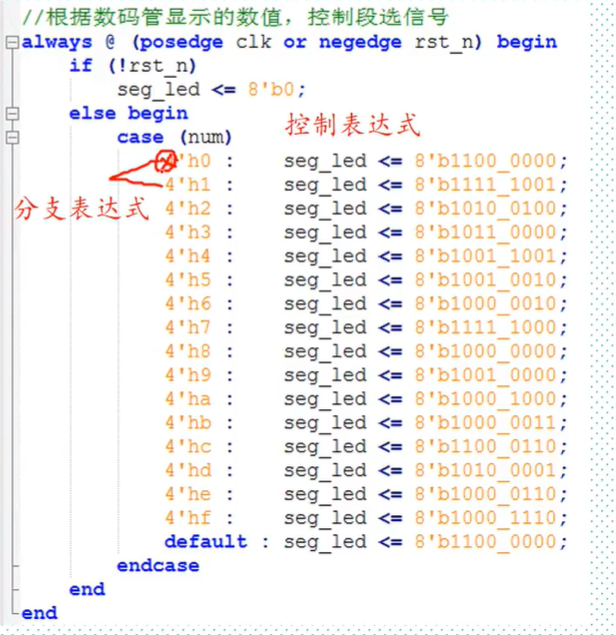

参数传递

除了从端口中将信号连接起来之外,也可以传递参数(parameter)

always/initial语句

简介

其中包含的为过程块,在过程块中可对变量赋值

不允许在多个always中对同一个变量赋值: 多个always并行性

不要混合使用阻塞赋值非阻塞赋值

条件触发

always @(posedge sysclk or negedge sys_rst) begin ... end

@(..) 成为敏感列表

时序逻辑

边缘触发往往为时序逻辑

非阻塞赋值: 计算RHS在先,只有在过程快结束时才更新LHS—一般为时序逻辑

组合逻辑

电平触发往往为组合逻辑

在组合逻辑中@( * ) 表示对过程块中所有变量的变化都为敏感的

阻塞赋值: 计算RHS(左值)并更新LHS(右值)—一般为组合逻辑

过程块语句

if ... else ...

只能在过程块中使用,如果需要包含多个语句 需要begin end(类似c语言的 { } )

if else 配对使用,只有if可能产生latch(锁存器)

latch只在组合逻辑中出现,会造成毛刺较多(???)

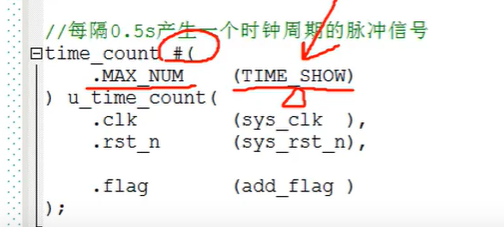

case( num ) ... endcase:

casez : 比较时候,不考虑分支表达式中z,其他位置相等即可

casex : 不仅z不比较 x值也不比较

分支表达式 和 控制表达式的位宽必须完全相等

casse的分支表达式没有给出全部可能时候,也会造成latch

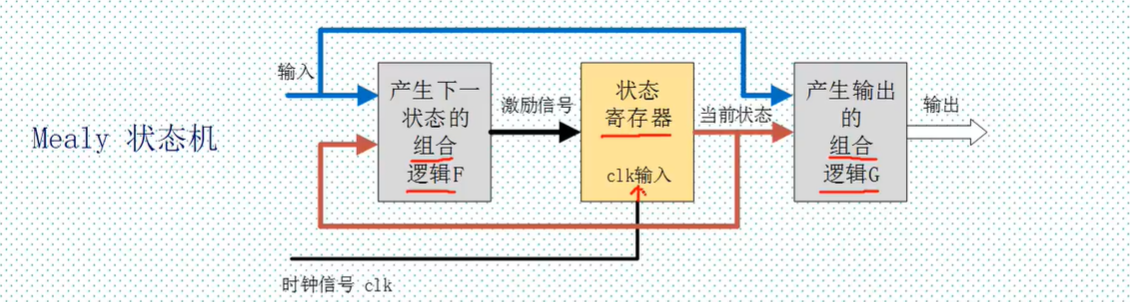

四.状态机

简介

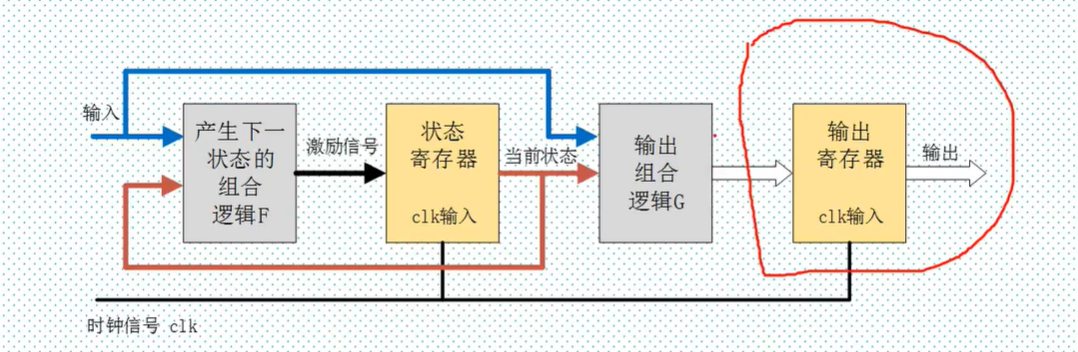

状态机模型中分为两个组合逻辑 一个时序逻辑

Verilog为并行执行的,不好做顺序逻辑

适合实现顺序逻辑: SDM控制器

状态机设计:

状态空间定义→状态跳转→下个状态判断→各个状态动作

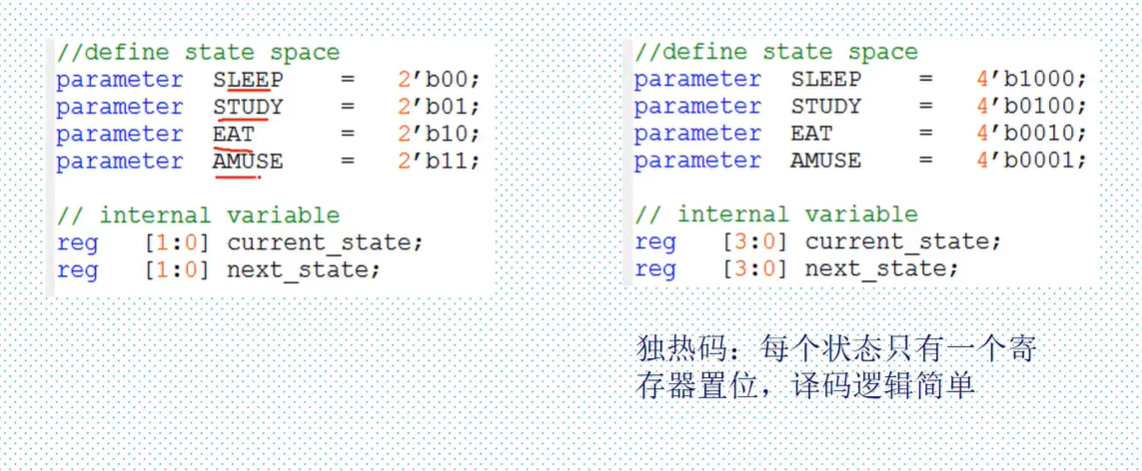

状态空间定义

二进制表示: n位代表2^n状态

独热码: n位代表n个状态 解码简单,FPGA占用资源小(推荐)

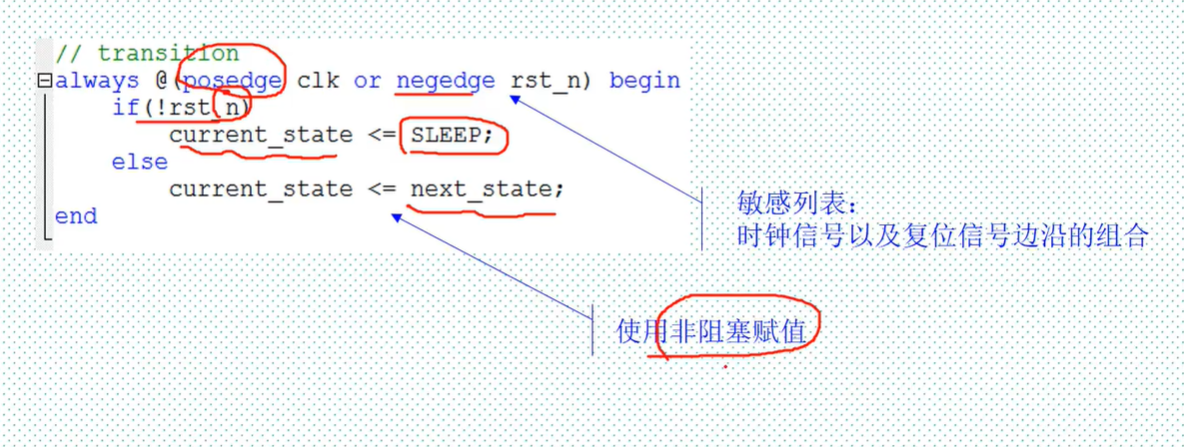

状态跳转(时序逻辑)

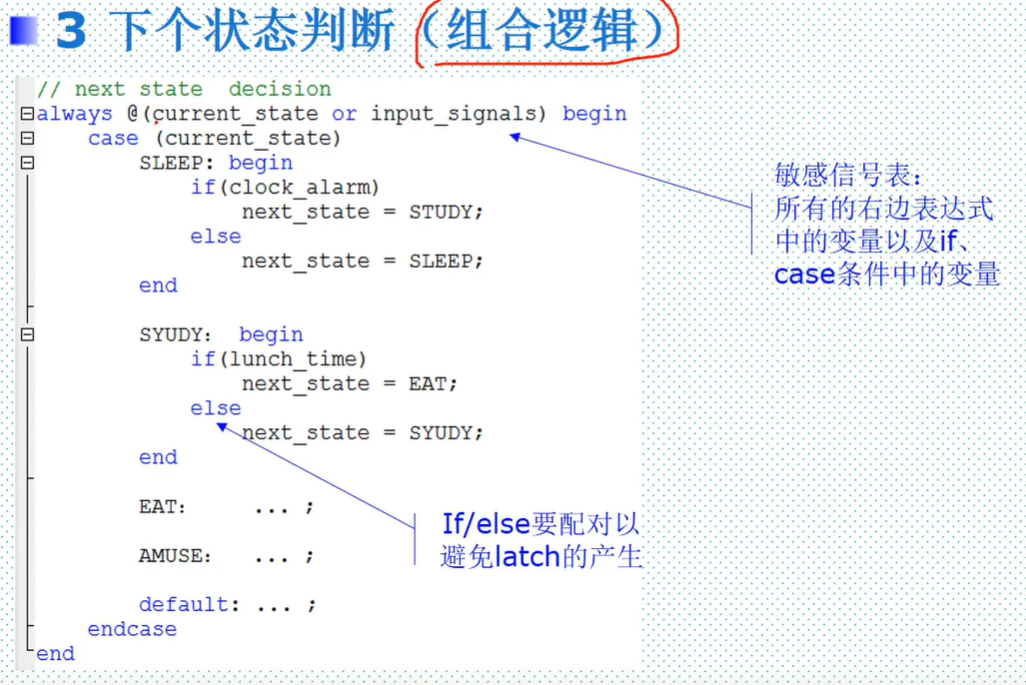

下个状态判断(组合逻辑)

敏感列表包括: 当前状态+外部输入信号

根据case( current_state ) 分配下一各逻辑

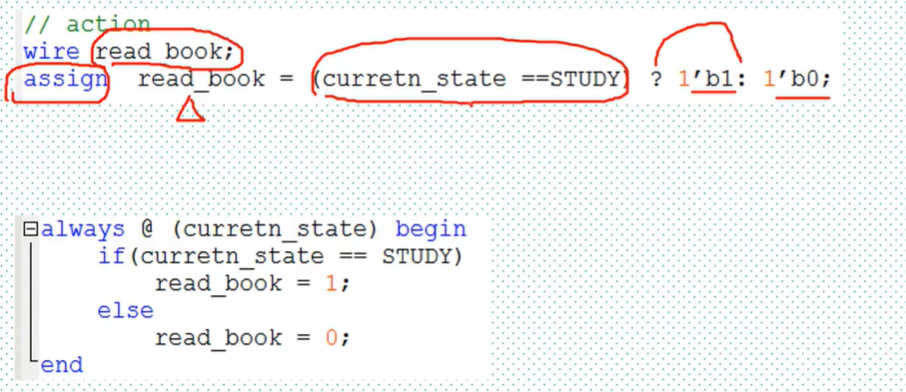

各个状态下动作

assigned 方法

always 方法

状态机扩展

当输出为多位时候(总线形式),可能某些信号先变化,有些信号后到,再加一层时序逻辑,来确保总线信号对其,仿真接收端采样出错

可以有效进行时序计算和约束

过滤组合逻辑输出的毛刺

五.简单实验

LED点灯实验

LED驱动方法

直接驱动

三极管驱动

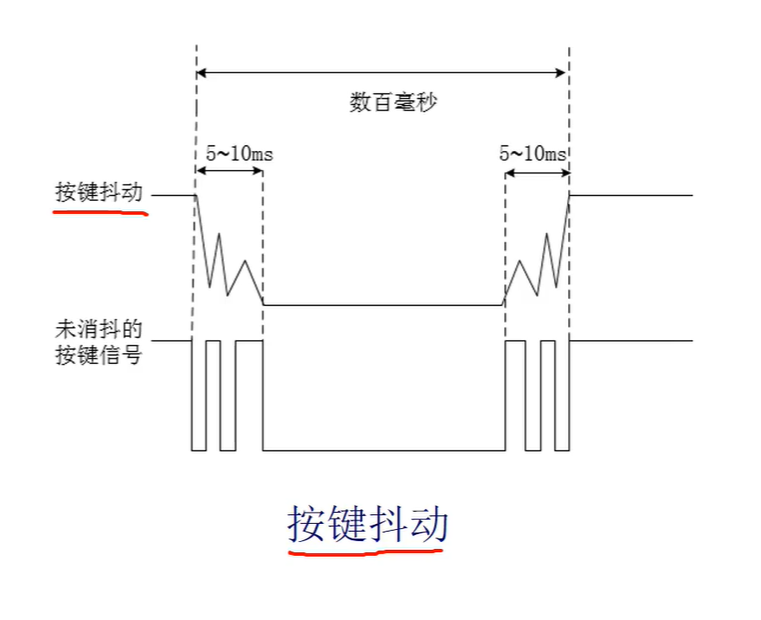

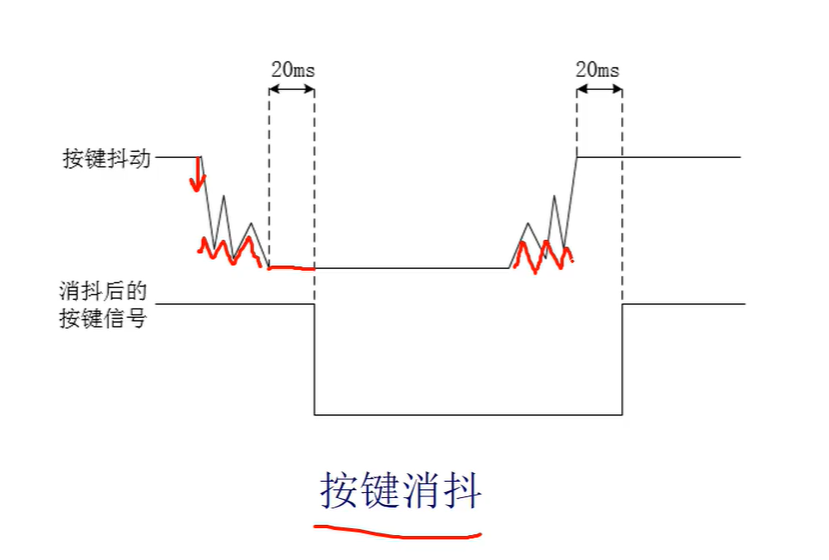

按键实验

按键消抖设计思路