一.综合简介

SoC简介

跟版上系统对比,把各种模块集成到单芯片上SoC解决方案成本更低

ASIC-SoC:

SOPC(System on Programmable Chip): 纯FPGA搭建的系统,软核microblaze && NIOS II

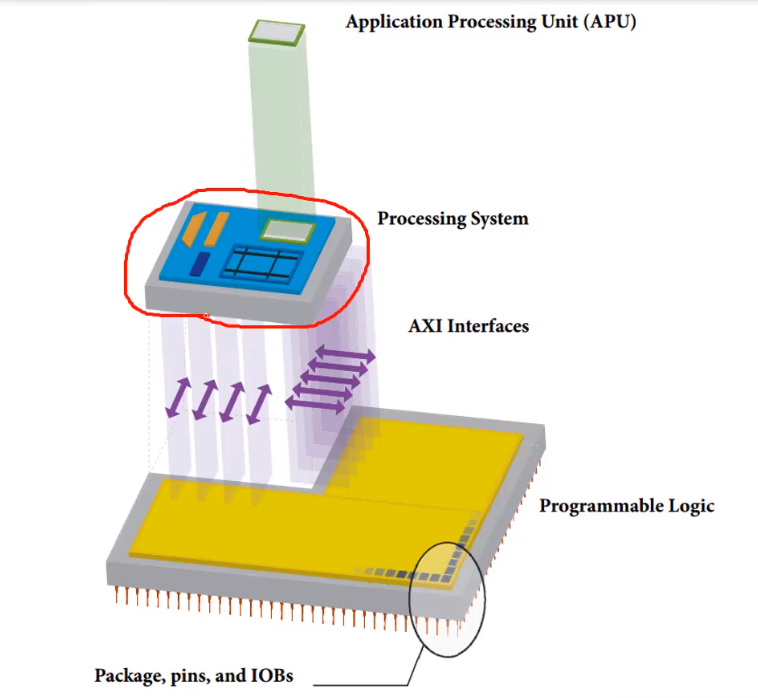

APSoC(All Programmable SoC): 存在处理器软件软件可编程 FPGA硬件可编程

二.Programmable Logic

可编程逻辑器件(Programmable Logic Device PLD):

允许用户电路修改内部连接

PLD内部电路结构可编程,可擦除重写

常见PLD

CPLD(Complex PLD): 基于乘积项与或逻辑阵列

现场可编程门阵列FPGA: 基于查找表(Look Up Table LUT)的 可配置逻辑块(Configurable Logic Block CLB) 阵列

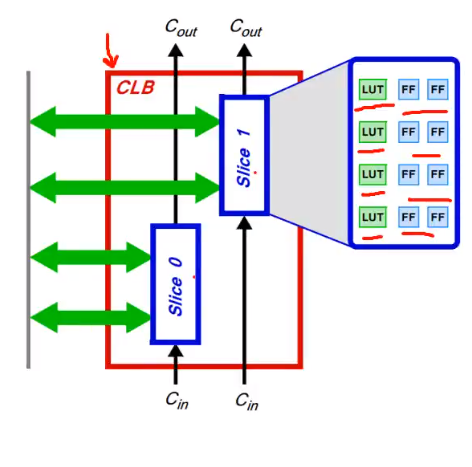

CLB单元构成(Xilinx 7系列)

两个Slice

每个Slice含有4个LUT和一些触发器

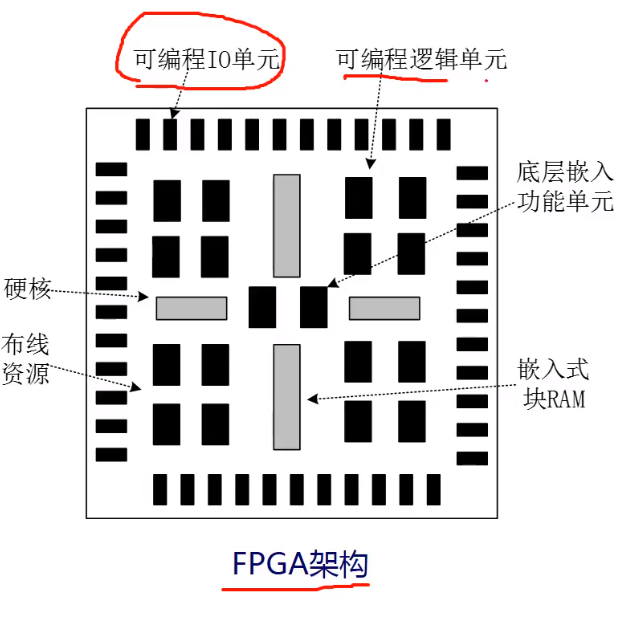

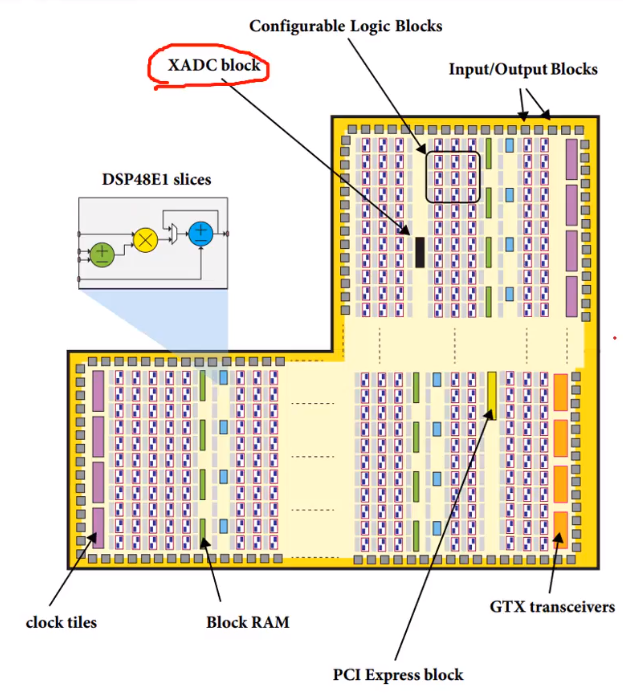

FPGA架构

可编程输入逻辑: IO-BlockDDR双倍速率 串并转换

可编程逻辑单元

硬核: XADC

底层嵌入单元: DSP 锁相环PLL

嵌入式RAM(Block RAM)

布线资源

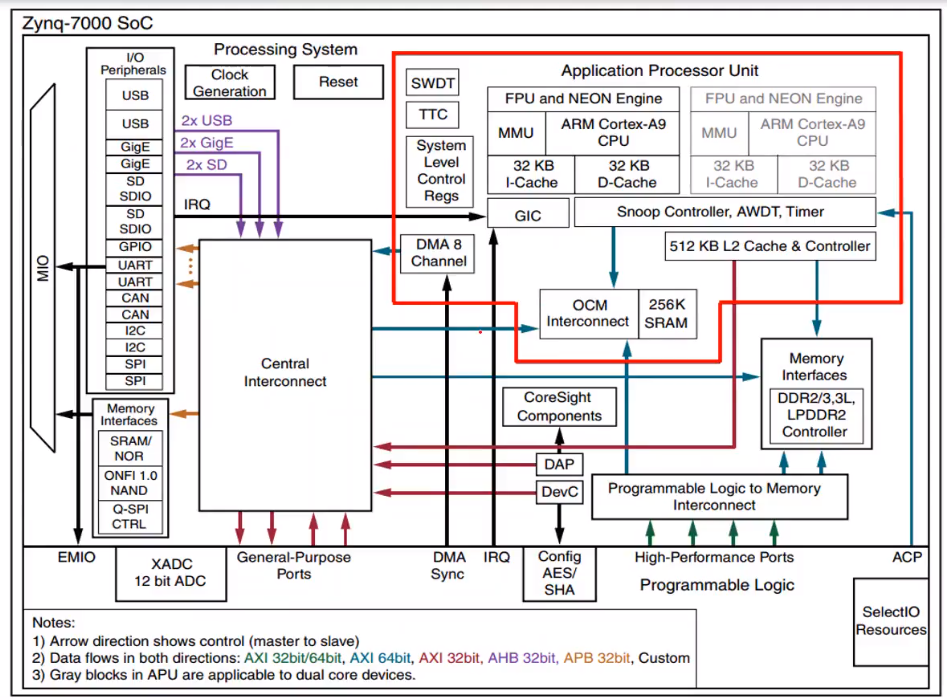

三.Process System

应用处理单元APU

双核ARM Cortex-A9

FPU浮点单元: 浮点运算加速

单指令多数据NEON引擎: 比如视频中对每个像素的并行处理 比如FFT

MMU存储管理单元: 物理地址到虚拟地址映射

指令Cache 数据Cache : 为L1 处理器独立

Snoop Control Unit 窥探控制单元:

维护不同核的Cache一致性 控制L2-Cache OCM片上存储器

DMA

中断控制器GIC

APU之外

中央互联器 OCM互联 PL互联

外设接口→MIO映射复用(区别于PL的IOBlock)→Pin(54个)

动态存储器接口: DDR2/3 静态存储器接口: SRAM Flash

时钟生成 复位模块

PS到PL接口

EMIO: 可连接到IOBlock 最简单的将IOBlock用作PS的引脚

Conifg AES/SHA配置接口

XADC: 12位

DMA

IRQ: 连到GIC中断控制

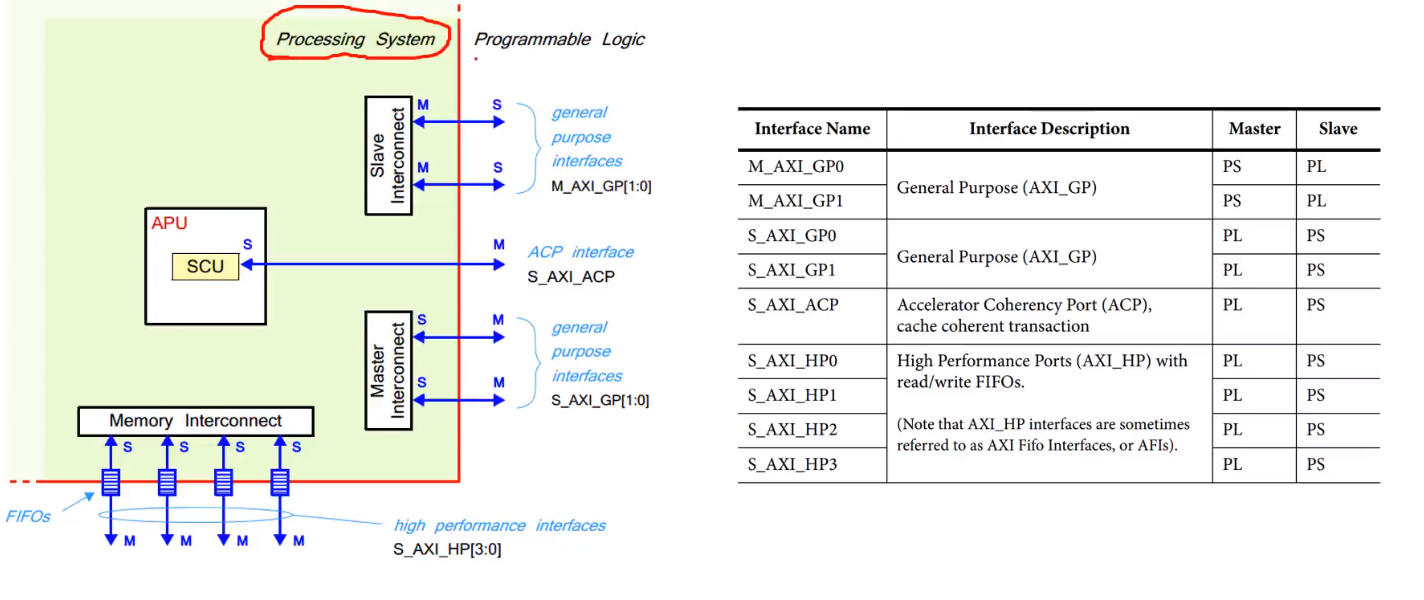

AXI (Advanced Extensible Interface)

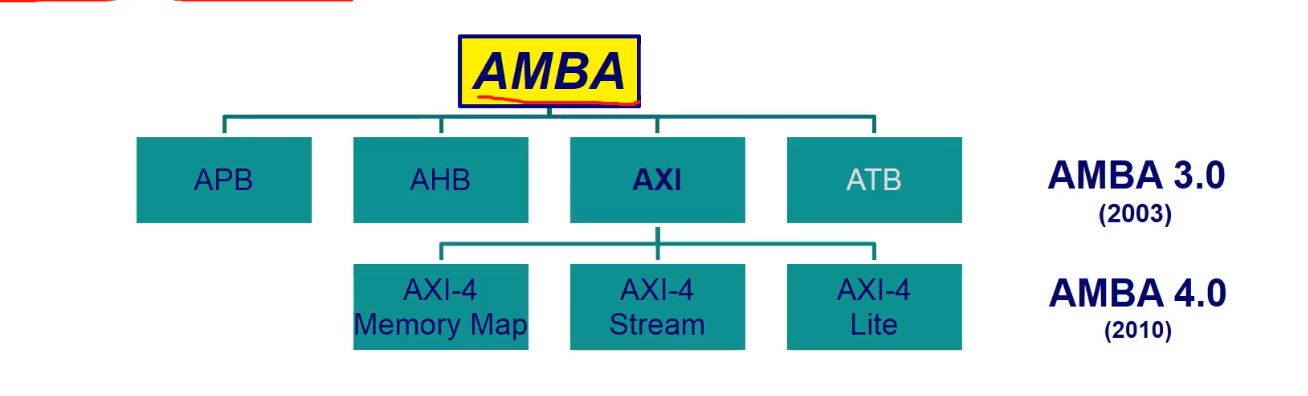

AMBA简介

属于AMBA: Advanced Microcontroller Bus Architecture

AXI组成

ACP:

PL均位主机

直接连接SCU 实现PL到L2的访问,实现PL到PS低延迟访问

General-Purpose Ports

Master: M_AXL_GP[1:0] PS作为主机

Slave: S_AXL_GP[1:0] PS作为从机

High Performance Ports:

相对于GP而言,PL均位主机

存在Buffer FIFO,以实现高带宽

四.开发板介绍