一.三极管对比

三极管相同:

三个电极,电极间导电能力由载流子浓度确定,载流子浓度缘由另一极电压决定

三极管不同之处

机理区别:

集电结反向电压,结电流几乎为0 发射结正向,但电流被集电结吸引

二者均有饱和区,但三极管饱和表示过大导致下降 FET表示达到放大区(载流子上限)

饱和即意味着,自变量变化时候,因变量不怎么变化

对于BJT和FET而言,这个因变量为集电极电流 栅极电流

对于三级管而言,因变量为,在饱和区时候,增大,不会改变

机理: C极对 B-E结正偏的多子吸收有上限

意味这,三极管在线性区中,不同几乎不影响线性区斜率(相对于FET)

对于FET而言,自变量为

机理: 在门限区下,沟道已经形成,升高会破坏沟道,大于时候沟道再次被破坏

同样,在电流不变区域下,比起BJT,其更加"平" (更大)

放大类型区别:

FET更接近理想得跨导元件(输入V输出I),三极管则受Early效应影响(厄利电压)

不能看作电流放大器件,因为输入阻抗无穷大

数学模型区别:

I_D随V_{GS}变化缓慢得多,是二次函数关系

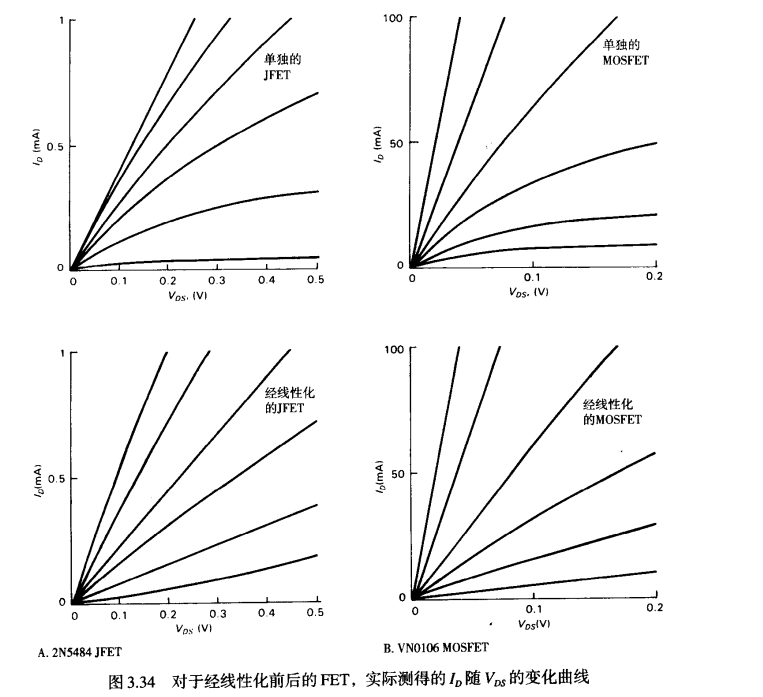

线性区饱和时有类电阻效应.效应R_DS与V_GS精确相关

容易被静电损毁

参数浮动更大,一致性不如三极管

跨导数量级分析

假设一个JFET BJT在共源(发)电路中,工作电流1mA,源(集电极)电阻=5K,10V电压供电

BJT:

JFET:

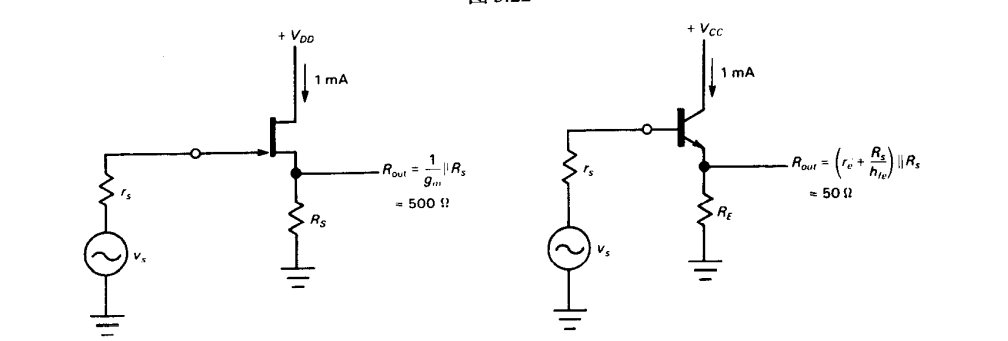

输入输出阻抗

输入阻抗: JFET=

输出阻抗: JFET= BJT= (同相关)

一般而言 BJT的输出阻抗比较低(25-75Ω)

当时候FET的输出阻抗比较低

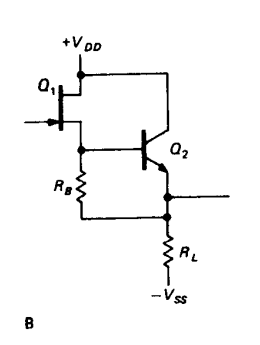

可借助FET的高输入阻抗 BJT的高放大,高输出阻抗 设计混合跟随器,详情参照下图的电路分解

二.模型分析

MOSFET(金属-氧化物-半导体)/JFET(结型)

对于MOSFET: 当时候导通,但如果在半导体掺杂,则可在的时候也可以有导通电流

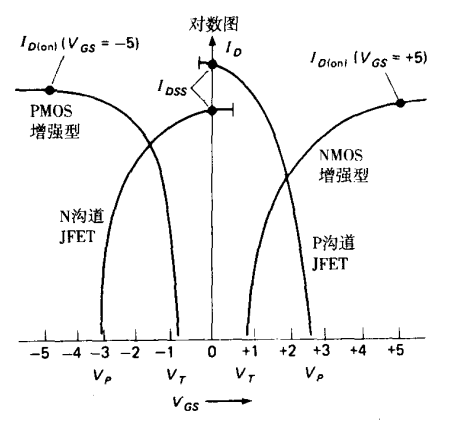

虽然理论上有耗尽型MOSFET但很少见,JFET全部为增强型(若不为,高出0.5V则PN结直接导通)

故只需了解 增强型MOSFET 耗尽型JFET

数学模型

MOSFET/JFET差异基本参数

二者基本为平移关系(注意N沟道JFET不能高于0.5V否则PN导通)

门限区()

线性区:

饱和区可令因为后再增加电压对影响不大

则有饱和区:

可以发现线性区不严格线性(存在)→但有电路可以解决

亚门限区

则有在亚门限区有 此常数一般为60

温度系数

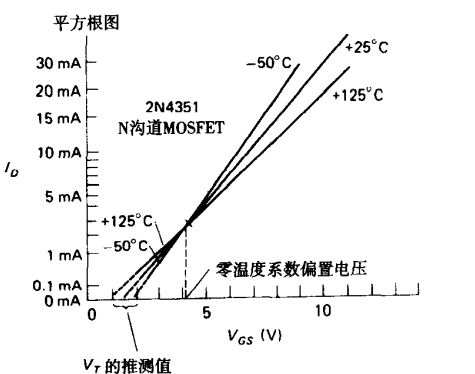

则有

但门限电压也会变换() 且有

两个作用此消彼长,较小时候,有个正的温度系数较大时候有负的,某一中间值温度系数为0

故较大时候,不再有热漂移,无需像三极管一样加集电极电阻(电流补偿)

制造偏差

以VN01(经典N增强MOSFET为例)

浮动0.8-2.4V(50%中值浮动) (1mA) 而三极管只有浮动0.63-0.83V(10+%中值浮动)(1mA)

意义:

虽然可以制造很好的电流源,但电流大小不可控

满足不了差分电路一致性的需求

改进

温度-梯度抵消法

共IC基地

最好可用的的FET对管差异仅为5mV 温度系数

最好可用的的FET对管差异仅为5mV 温度系数

和BJT的比较

四.FET电容效应

栅极电流()(直流特性)

定义 : Broken Volt 击穿电压为时候的 (直流效应)

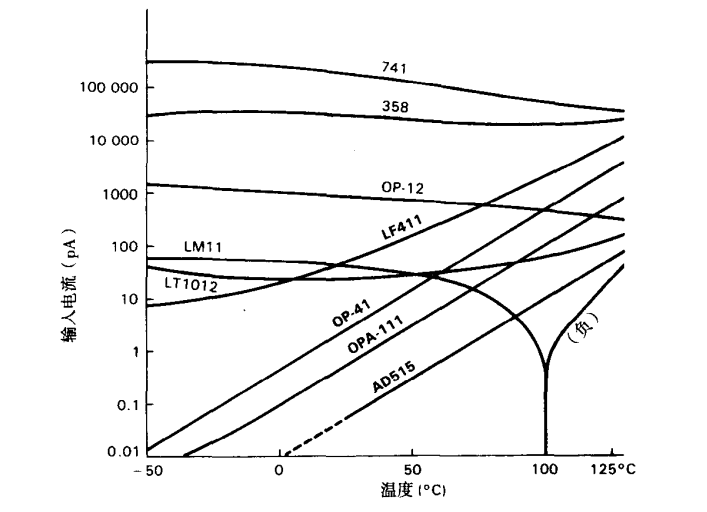

考虑集成电路中往往不怎么区分BJT FET 用(中文: 输入偏置电流)代称

的温度特性

受温度特性影响很大,甚至大于BJT,同I_D受温度特性影响相对小不同<见温度系数>

经验上: 每上升10℃ 近似加倍

图中表现较好的 精心设计BJT: LM11 LT1012 和 FET: OPA111 AD549都比较昂贵

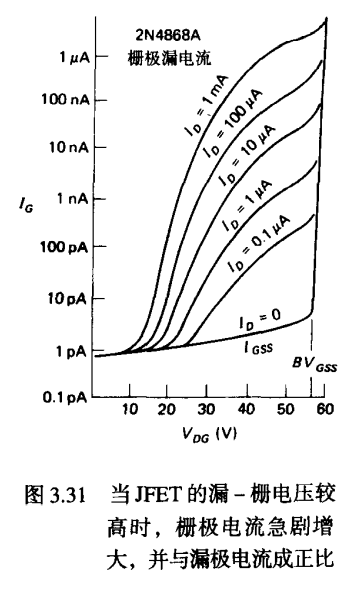

JFET 碰撞-电离电流

对于JFET,还存在碰撞电离电流,和相关,再未达到之前也有较大的电流

改进

改用MOSFET

使得变小

或者用栅地源地放大器(???)

动态栅极电流(交流特性)

典型分析1

设信号源为100k内阻

假设输入电容为5pF,在 1MHz 下电导为5m

换算一下,阻抗为20k(课本为30k)

需要控制在低阻抗(50),FET不能视作阻抗

典型分析2

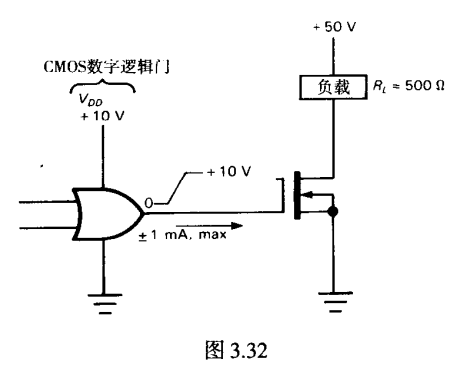

数字逻辑电路(0-10V 1mA输出能力)驱动功率MOSFET(50V电源 500负载 10A电流)

1mA输出,带来接近20s转换时间(10V)

可能由于SCR封锁,破坏前级电路(???)

需要控制输出电流接近500mA可用达林顿复合实现

响应速度

由于和电容和存在,存在限制因素

而且低的一般高

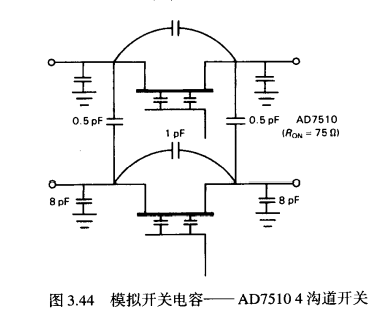

FET电容模型

电容模型: 输入到输出沟道到地到其他FET

如何计算反馈db(已知f C 负载R)?

级联开关: 减小C_{DS} 增加R_{ON}和衰减

对地电容

高频近似导线到地,则有分压—即高频衰减

课本例题反馈不会算 ...

感性负载问题

一个电感L作为负载,会和 栅-漏C 构成串联,使得有一个选通滤波器

快速变换漏极电压产生瞬态栅极电流,破坏CMOS

变换使得

且有反馈电容(相对较小 典型值5pF): 但在共源放大器中占主导位置(米勒效应)

可在电平输出-栅极 中加入电阻,速度和保护中取得平衡

五.实用电路

效应管开关电路

相比晶体管,不需要电流输入,直接给出所需得电压即可

可用于模拟开关

G上电压比输入还要高时候才能确保打开,或比两端电压更负才能关闭

随着信号得变化而变化(相关)

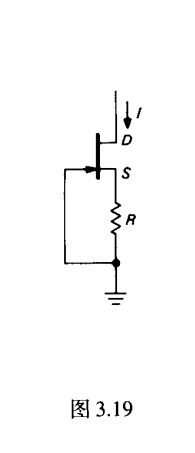

JFET电流源

无偏置

直接将JFET的栅极同源极相连,只需要一定的V_DS则有良好的电流源特性

但是电流大小不可知(制造偏差)

可用于三角波发生器

源极自偏置

可调节电流

显然V_GS比原来更小,故I_D会变小,可根据R阻值来调节

注意:每个JFET制造偏差,统一源级电阻可能导致不同电流源,要逐个分析,或者使用可调电阻

更好的电流源特性(高输出阻抗)

反馈思想: 电流感应反馈(? ... )

VI叠加法,但DS视作二端元件(并联电阻电流)源,加串联电阻,显然VI图上编译更小

同BJT电流源的比较

双JFET串联

显然具有透传电流的特性

注意:显然有 由于则有故需要更大的

为何受负载影响小: 且有 故 而受电流变化很小,故

JFET放大器

输入阻抗无穷,只能通过跨导分析

小信号下为

由于输入阻抗为无穷大,所以只能采用

本征模型 而不能采用 Model

为何放大倍数不如BJT

对于BJT其

对于FET其在门限区为

对于相同的电流.FET所需电压大得多,所以本征较大跨导小

而放大倍数为所以放大倍数小

对于典型数值

BJT: 10V-VCC 1mA静态电流 则有

FEt: 同样10V-VCC 1mA静态, 同样计算得

JFET跟随器

输出阻抗分析

BJT: 采用本征模型 则有

FET: 采用本征模型 则有

G_v分析(跟随效应)

思路1:

则有

得到

得

当时候取得最佳近似

思路2:

即为和的分压

输出电阻为 主要取决(在1mA时候为500-不如BJT)

缺陷分析

如上述思路2分析,恒压特性不如BJT(通过BJT FET混合电路解决)

或者开启电压制造偏差大,直流偏置不确定

BJT混合改进有源负载-跟随器

可以利用FET的更高输入内阻和BJT更低输出阻抗

通过V_BE的压降固定来提供有源负债

如果只单看电阻,以为是的恒流特性导致的电阻大则不对

电阻变小,证明: 考虑曲线,并联R等效提高了斜率

但是接下来串流的电阻由于增益所以使得还是近似于

总体抽象来看,还是可以视作为恒流源

缺点

V_{GS(th)}的开启电压还是不确定

匹配FET跟随

常常被用作示波器垂直放大的输入级

常常我们思路为先确定再确定

但此处不同

我们可以确保两个相同,手动偏置其中一个

另一个必然也与我们反控相同

更好的是由于小的I_D区别 V_GS区别不大

类似FET电流源,加入减小因引起的I_D偏差,同时设置获得更好性能(???)

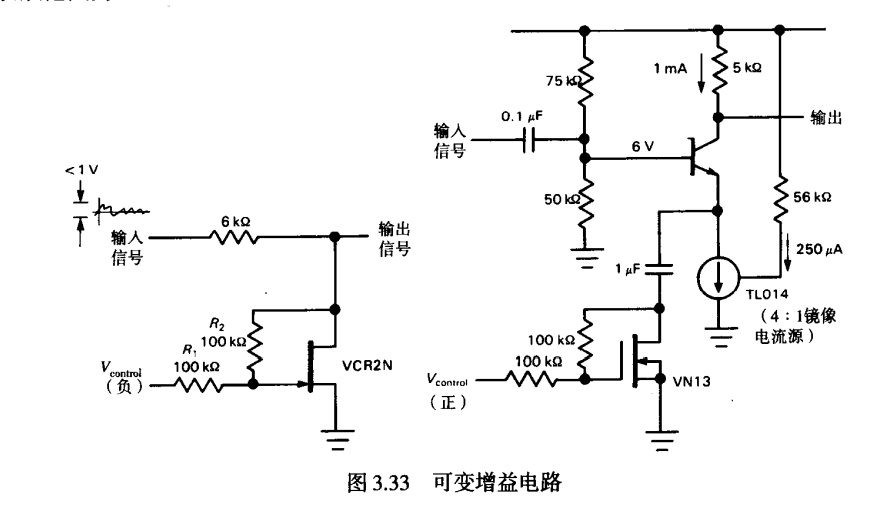

可变电阻

非线性区改进

原理: 使得加上一半的偏置,即可

应用,用在三极管放大器的射级电阻上调整增益

直流偏置本质上是一个加法器,只不过加法器一端为恒定电压,输出电压=输入+偏置

电容法: 通过在分压器输出点添加一个电容,来做到直流偏置

浮动GND法: 通过分压网络中分压点的线性叠加关系,来求取线性叠加或偏置问题

模拟开关

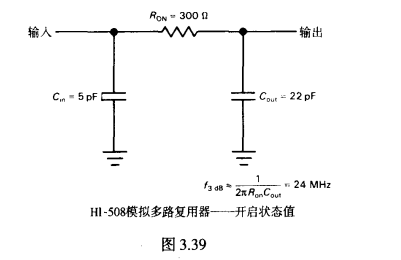

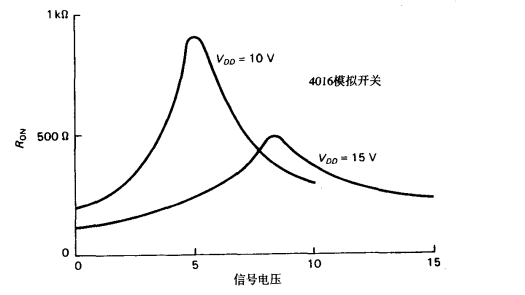

典型值为30 最差为75

简单N沟道开关

需要将V_G设定为系统最高电压-最低电压

对于10V输入V_G最好能在15V左右,使得R_{ON}降低

需要一个旁路电阻(负载电阻)以减小开关关闭时电容的影响(降低以换得更短微分响应)(???)

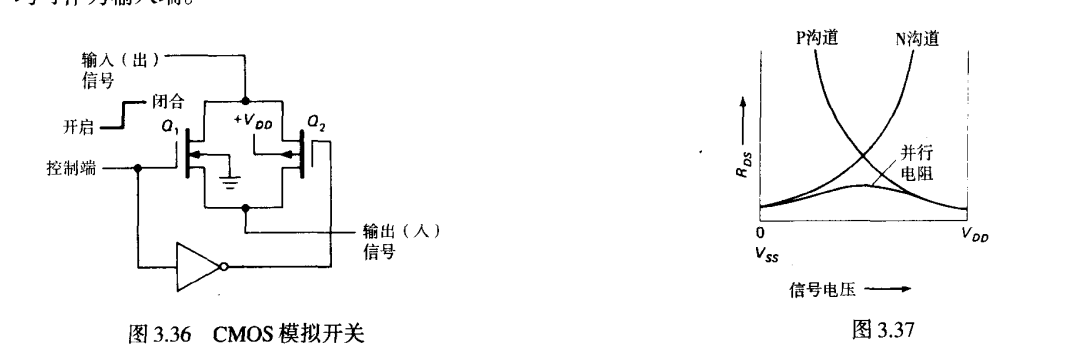

CMOS线性开关

当接近原来的V_CC时候,变大,不适用开关所需的低电阻

对于N沟道为不够高 对于P沟道为衬底电压不够高

可利用互补互联型MOSFET开关

分析(???)

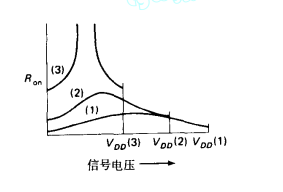

关系总结:

不仅和相对相关,当V_{DD}越大时候,整个信号区间都有较小的

且当为时候有最大值

且有

而至少为有几V

则有时候取最大无穷阻抗

不能解释:

为何增大后收敛了

为何有最大值

正确解释

当栅源电压从高向低变化的时候,NMOS的导通电阻逐渐变高.而PMOS的导通电阻是逐渐变低的,CMOS的导通电阻可以看作这两个管子的并联

那么在这个过程中就必然有一个极值

对应着就是电源电压的中点,也就是两个管子导通电阻相同的时候。

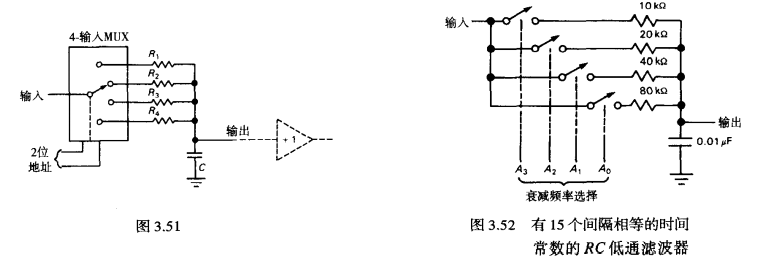

多路复用器

比如模拟信号的轮流采样

构成可积分电路(非RC近似积分) 采样保持电路

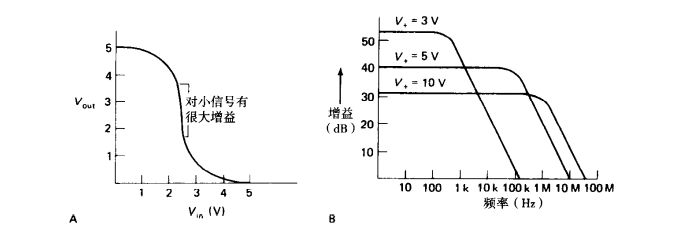

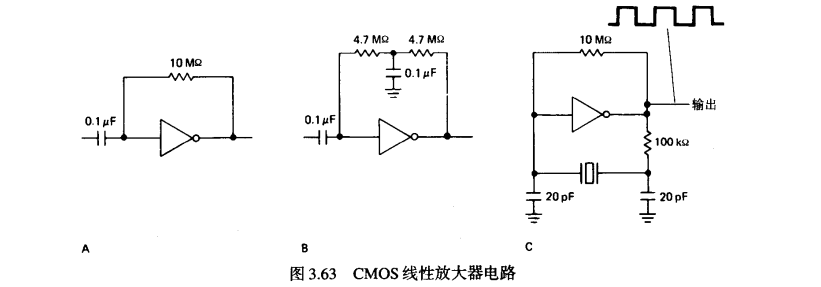

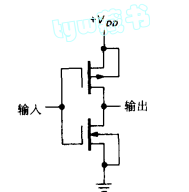

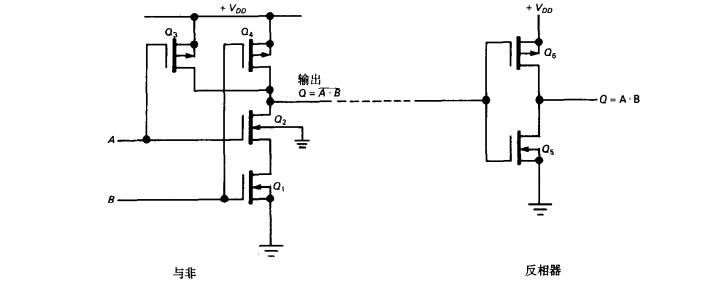

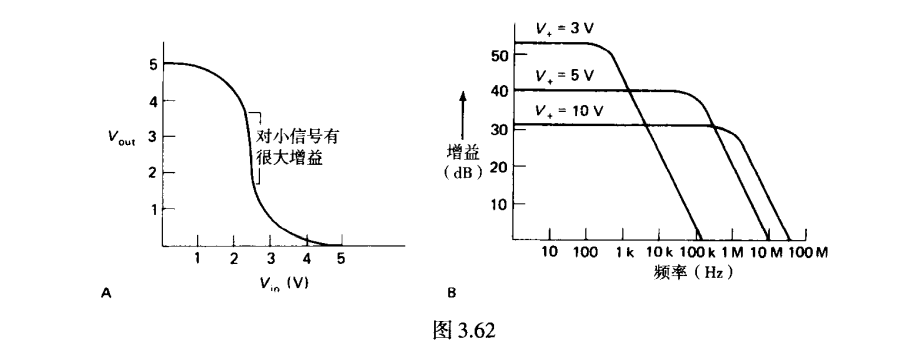

CMOS反向放大器

考虑CMOS反相器(类似于推挽跟随的结构,但是有极性相反)

把FET互相看成对方的有源负载,可得到如曲线

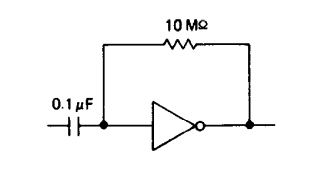

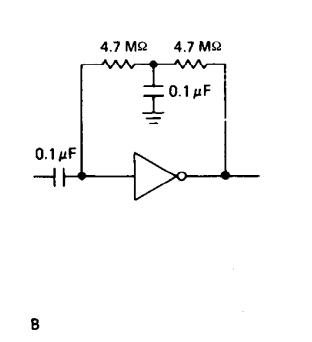

要使得有个偏置使得信号中点在处可将大电阻从输出接回输入

图B: 可通过旁路来减少输入阻抗

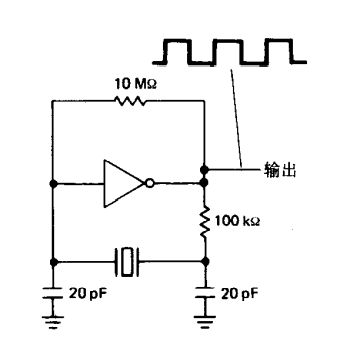

图C: 晶振 待研究...

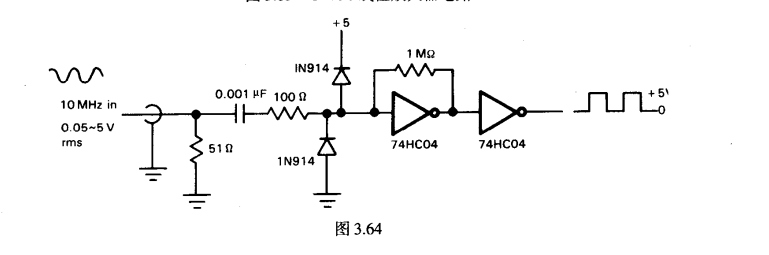

既可以用上图的两个普通二极管,使得电压>5.7V时候上管导通,也可使得<负0.7V时候下馆导通

也可只用下管,但为稳压二极管(非交流信号状况下),交流下失效,稳压二极管动态阻抗有限,无法钳位

四.其他实用电路

可选时间常数的RC滤波器(基于多路复用器)

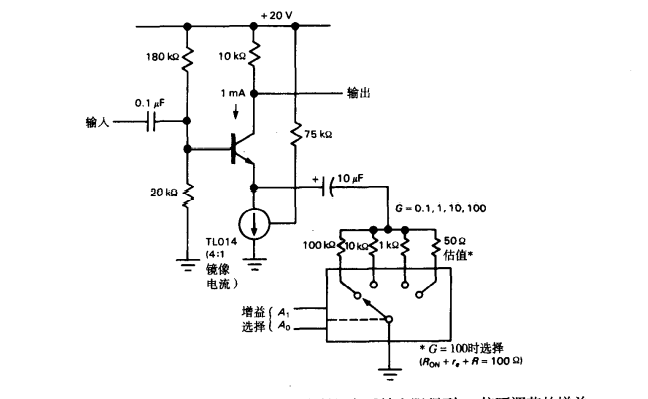

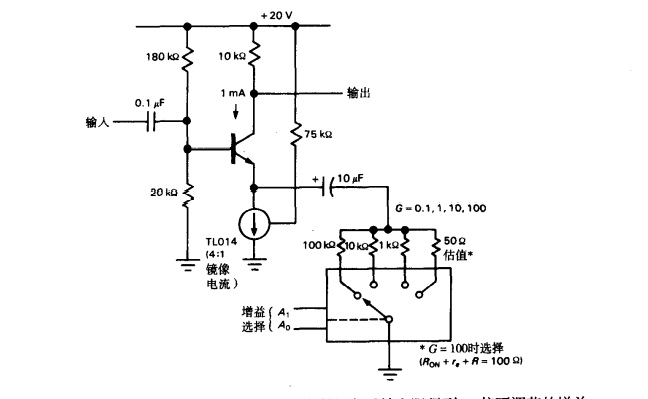

增益可选放大器

电流源提供良好的直流偏置

采样保持电路

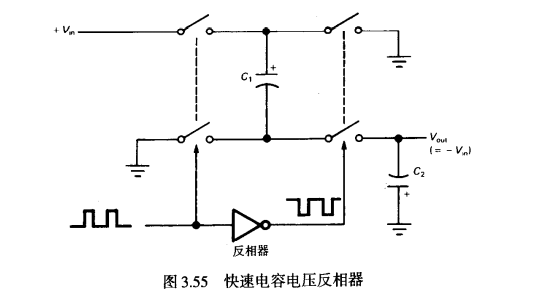

快速电容反相器(电荷泵)

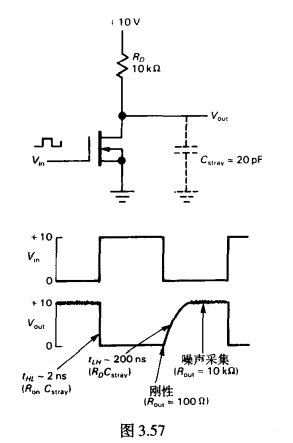

MOSFET反相器

问题1: 静态功耗 负载功率的矛盾问题

需要低静态功耗,则需要大的电阻

但是偏置电流小了,能输出的电流只能小于输出电流

问题2: 关闭MOSFET的时候高输出阻抗和杂散电容构成积分器

为何下降沿没有: 下降沿低阻抗,构成的时间长度短

上升沿电阻比较小

解决

设计CMOS逻辑门的通用方法

利用开关并联串联带来的AND OR特性

保证强逻辑

缺陷

并非0功功耗,电压转换时由于,有个瞬态电流

由于CMOS里面太多栅极,每个都有电容,所以转换时候一定有耗散电流

或者推挽MOSFET,一段区域内都导通,大的电流通过

CMOS线性放大器

将推挽互补CMOS其中一个看作另一个的有源负载

当输入取 和 地中间时候对小信号有很大的增益

而将原本的用途-反向器输出的恒定电压视作削波

为了使其线性放大,需要加偏置来到放大区

直流反馈

大电阻 连回输出输出

(输入输出曲线的交点恰好为放大区,且有输入阻抗无穷大)

电容电路

提高信号频率下的输入阻抗

功率MOSFET

相当于多个MOSFET并联,使得更高导通,更低

典型值

优点

低输入电容: 1.并联 2.考虑电容制衡关系

高输入阻抗

热稳定性:

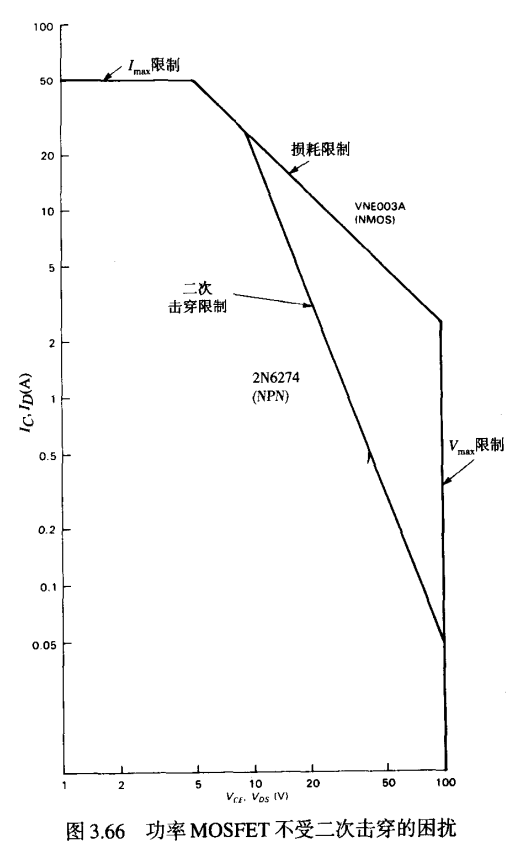

二次击穿效应

无三极管二次击穿特性(有正温度系数导致正反馈)

局部过热点更高电流密度→"电流错乱"导致热损耗→二次击穿

故三极管安全工作区电压()小于晶体管的功率允许范围

MOSFET优点

故MOSFET也不需要射级限流电阻来减小温度影响

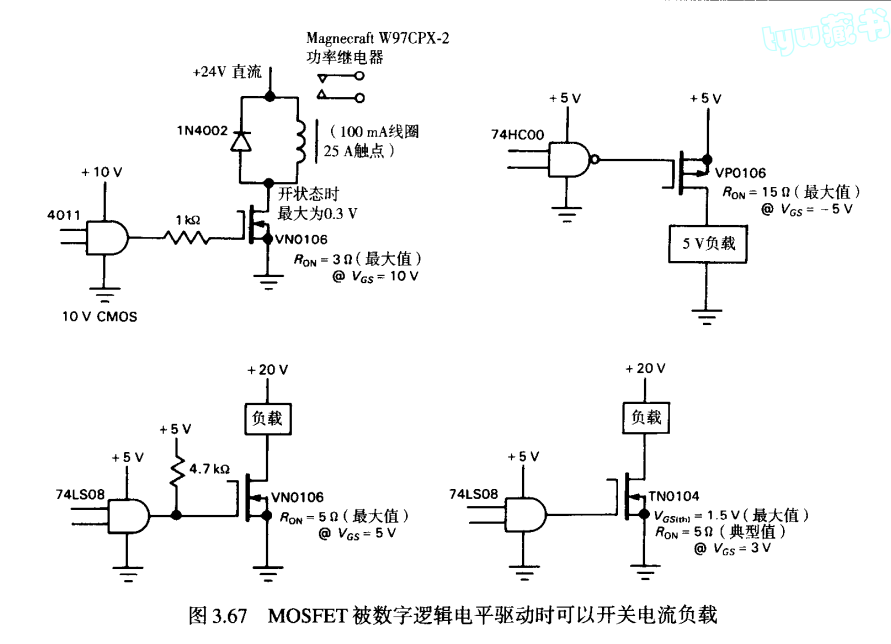

数字逻辑控制功率MOSFET

常见数字电平有5V(高速CMOS) 和TTL(2.4V)

MOSFET选择策略-10V(高电平)

随便MOSFET即可,VN106可以保证时候

不需要射级电阻,但仍然有用,止负载的暂态感性耦合到CMOS逻辑

5V电平

可选VN01/VP01系列

TTL电平: 一般为3.5V很少低于3V

可选专门为逻辑电平设计的功率管

如VN0106: ,但是若要驱动I_D=1mA,则要更高 且有时候,